文 | 芯东西 ZeR0

编辑 | 漠影

芯东西3月3日消息,全球三大芯片制造商英特尔、台积电、三星,封测龙头日月光,以及x86和Arm生态的顶尖芯片设计公司AMD、Arm、高通,谷歌云、微软、Meta等科技巨头强强联手,推出了一个全新的通用芯片互连标准——UCIe!

UCIe网站:https://www.uciexpress.org

该标准专为chiplet(又名芯粒、小芯片)而生,希望为封装创新构建一个开放的chiplet生态系统,不仅简化所有相关环节的流程,而且提供跨芯片制造商、跨制程节点的芯片产品,让不同制造商的chiplet之间的互通混搭成为可能。

过去五年左右间,chiplet逐渐成为芯片设计业的一个主流趋势。它通过die-to-die互连技术,将多个满足特定功能的不同模块芯片,像搭乐高积木般进行组装,从而构成一个具备多种功能的异构芯片,有助于解决芯片制造成本、芯片设计整体可扩展性等诸多问题。

如今,经过多年磨砺后,这一技术终于迎来里程碑时刻——英特尔、AMD、Arm、日月光、谷歌云、微软、Meta、高通、三星、台积电联合起来,正在打造一个新的开放芯片互连标准UCIe,且UCIe 1.0规范现已发布。

值得注意的是,英伟达并未出现在这个联盟的成员名单中,我们也暂未看到RISC-V的身影。

01.发展chiplet互连标准是大势所趋

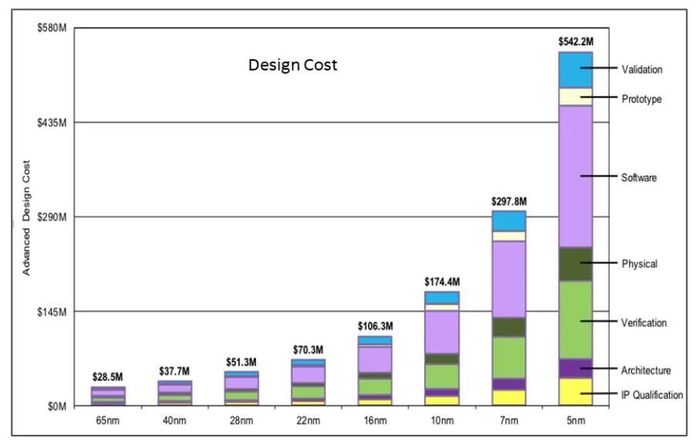

在摩尔定律日渐式微的背景下,芯片制造商正努力应对日益困难的规模问题,通过降低成本、在单个封装中使用不同类型的工艺节点等方法来继续优化芯片,能缩短整体芯片开发生产流程、降低成本的chiplet渐渐走向主流。

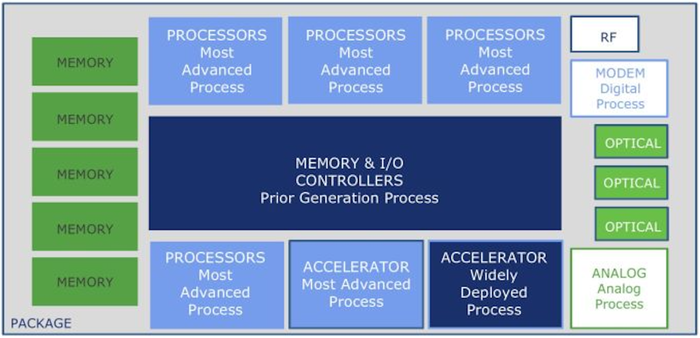

借助chiplet技术,一个大型芯片不需要全部使用昂贵的7nm、5nm等先进制程,而是可以根据自身需求,混合搭配由多个芯片制造商、多个制程节点制造的芯片模块,将它们封装在一起。这样既有助于提高效率,又减少了经济负担。

对性能与效率的追求,也驱使人们对chiplet产生持续的兴趣。PCIe按照芯片标准来看偏慢,延迟较高,且数据传输能耗偏高,因此芯片制造商希望将更多功能集成到芯片中来降低延迟和功耗。

如果用chiplet实现,这或许能将性能提高20倍以上,或者将功耗降为原来的1/20。

然而chiplet之间缺乏标准化的连接,市面上有大量定制的专有互连,现代芯片很难实现与其他设计即插即用。此外,芯片设计和互连的标准化确认(validation)和验证(verification)长期欠缺,使得芯片生态系统无法实现。

这就是UCIe联盟想要做的事——实现chiplet(如核心、内存和I/O)之间的标准化连接。

02.分层协议,支持2D和2.5D封装

UCIe是一个分层协议,包含物理层、Die-to-Die适配器和协议层。

如上图所示,物理层可由来自多家公司所有类型的当前封装选项组成,包括2D封装、2.5D封装,如英特尔EMIB、台积电CoWoS、日月光FoCoS-B等方法。该标准未来也将扩展至3D封装互连。

在物理层,其初始规范列出了芯片将用于相互通信的电子信号标准、lane数量、凸块间距(bump pitch,连接密度)和沟道长度等指标。只要一个chiplet符合标准,那么它就能与另一个UCIe芯片互通。

UCIe 1.0规范有两个性能/复杂度标准级别。

“标准封装”级规范是为使用传统有机衬底的低带宽器件设计的。这些部件将使用多达16个lane、100μm+凸块间距以及扩展的沟道长度。这就像在一个当代PCIe链路上连接两个设备,但是把它们放置得非常非常近。

“先进封装”级规范涵盖了EMIB和InFO等所有基于高密度硅桥的技术,要求在25μm~55μm范围内的更小凸块间距。由于密度更大,每个cluster需要4倍的lane,且沟道长度小于2mm。

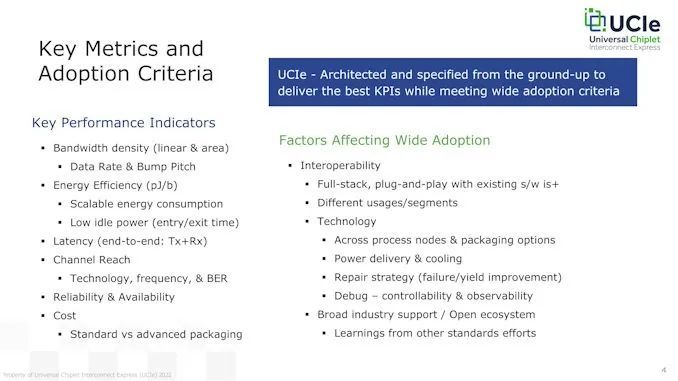

UCIe的推广者认为,如果采用目前的45μm凸块间距技术,先进封装装置将能提供高达1.3TB/s/mm的shoreline(线性)带宽。也就是说,每秒1.3TB的数据可以通过1mm的芯片边缘。

性能最高的设备通常都是将尽可能多的低延迟带宽塞进尽可能小的区域,但大多数设计不需要这种级别的性能,故而设计者可以使用多种手段来定制设计。因此,下图中“关键指标目标”部分将因不同的设计选择而异。

此外,该联盟在构建该规范时考虑到能效,适应了诸如快速开关(亚纳米秒)等高级功能。

Die-to-Die适配器为芯片之间的链路状态管理和参数协商提供了基础,并负责通过CRC和链路级重试为额外的数据可靠性保障提供可选支持。

03.借助PCIe和CXL标准还能用于芯片外的连接

新UCIe互连的外观和操作类似于on-die连接,同时还支持与其他组件的off-die连接。这些设计甚至可以为机架规模的设计提供足够低的延迟和足够高的带宽。

在协议层,芯片制造商有几种不同选择。

UCIe的官方标准协议是成熟的PCIe和开放的CXL(Compute eXpress Link,由英特尔发起)。

PCIe协议可提供广泛的互操作性和灵活性,已经成为各种其他技术的支柱;CXL则可用于更高级的低延迟/高吞吐量连接,如内存(cxl.mem)、I/O(cxl.io)以及GPU和ASIC(cxl.cache)等加速器。

客户和芯片制造商都可以利用他们在PCIe/CXL上的现有软件投资,进一步简化开发过程,并更快地推出符合UCIe标准的芯片。此外,联盟发起方已明确表示,UCIe不会局限于PCIe/CXL,其未来版本可能会添加其他协议。

与其他连接标准(如USB、PCIe和NVMe)一样,UCIe标准希望实现无处不在和通用,同时为芯片连接提供卓越的功率和性能指标。

UCIe的初始版本来自英特尔,过去几十年,英特尔主导开发了几种颇受关注的开放互连技术,包括USB、PCIe、和Thunderbolt 3等等。英特尔之前也为其EMIB使用了AIB(Advanced Interconnect Bus)和UIB两种协议。

在此前试图培养标准化的芯片生态系统时,英特尔发布免版税的开源AIB互连标准,但这没有获得足够的行业吸引力。相比之下,CXL当前已被广泛采用,因此将其与UCIe一起使用更有意义。

不过,UCIe和AIB并非天生兼容(特殊的子集设计可以同时支持两者),因此,虽然英特尔将继续全力支持当前的AIB实现,但它将停止所有进一步的开发并迁移到UCIe。该标准规范还包括一个Retimer设计,它可以将连接扩展至芯片封装之外,实现与内存池、计算和加速器资源等其他组件的光学和电气连接。

UCIe联盟设想了这种互连最终能实现芯片行业几十年来一直在努力构建的足够量的机架级分散系统。Die-to-Rack连接可以使用本地CXL进行PCIe通信(无需转换),可能最终提供此类设计所需的延迟和带宽,如有需要,还可使用其他类型的协议。

在开放计算项目(Open Compute Project),BoW(Bunch of Wires)规范也可被视作UCIe的一个对手。

BoW规范同样旨在使芯片设计大众化,并拥有令人印象深刻的性能规格,但它没有那么灵活。例如,BoW提供的能效范围是0.7~0.5pJ/bit(每位Picojoules),而UCIe提供的支持0.5~0.25pJ/bit,这可能因使用的制程节点而异。

BoW支持固定的16GT/s,而UCIe是可配置的,可扩展至32GT/s。UCIe在其他指标方面也领先,如Shoreline带宽密度(1280Gbps vs 3.8Tb/s),且仅限于MCP封装,而UCIe可以支持大多数2D和2.5D封装选项。

04.结语:UCIe刚刚起步但发起者已经看向未来

总体来说,UCIe规范旨在使封装互连看起来尽可能类似于on-die互连,同时提供大量选项,几乎可以实现所需的任何类型的性能或封装技术。

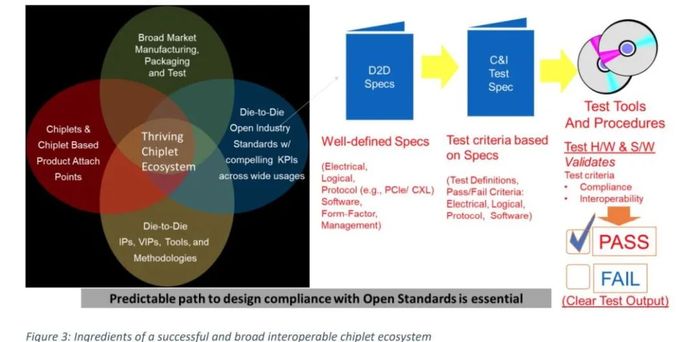

标准化互连是提高任何设备更广泛的验证、合规性和互操作性的第一步,而半导体行业长期缺少被广泛接受的芯片确认、验证和资格认证流程。UCIe联盟非常关注这些方面,初始UCIe 1.0规范有一章专门针对验证和内置功能来帮助这些工作。

UCIe联盟的强大成员公司们将开始开发下一代UCIe技术,包括定义chiplet form factor、管理、增强安全性和其他基本协议。他们还在寻找更多的成员加入,以期加速改变行业交付新产品的方式。

新标准不仅以开放的方式提供,而且其相关公司将在今年晚些时候成立一个正式的联盟集团来管理并进一步发展UCIe。

来源:UCIe官网,tom’s HARDWARE,AnandTech

评论