文|侃科技

半导体作为人类科技进步的技术核心,过去一直按摩尔定律前进。这期间因为智能手机芯片小型低功耗的特殊要求,又显著放大了制程微型化的作用。

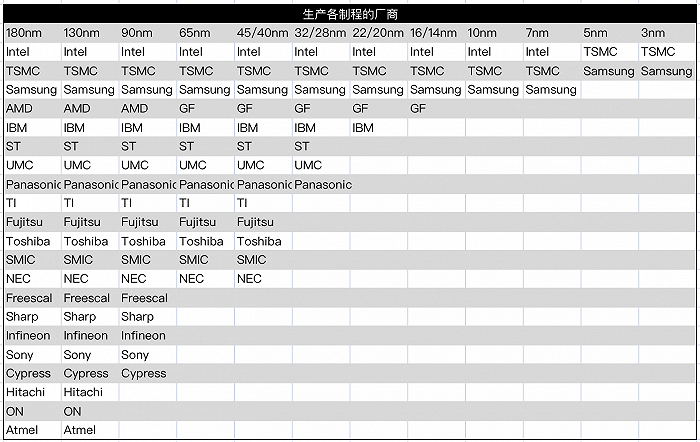

台积电就沿着晶体管缩小这条路径屡试不爽,始终保持着行业领先。从180nm到3nm,台积电用20年时间熬走了99%的竞争对手。尤其28nm后,在FinFET技术上逐步甩开竞争对手,14nm以下基本处于市场垄断地位。

但是,即便熬走了对手台积电还要面对一个更棘手的问题:摩尔定律的衰减,使得晶体管微型化变得越来越困难。

硅基半导体的技术演进,每18 -24个月晶体管的数量翻倍带来芯片性能提升一倍,或成本下降一半。十多年来,CPU和GPU的性能每两年多稳步提高一倍,而晶体管密度每三年翻一番,能源效率用了近四年的时间才达到这一目标,摩尔定律仍在前进但在明显放缓。

而且,终端市场需求逐渐从智能手机转向人工智能,这种转变又带来了一个看似相悖的现象:需求集中在云端的高算力AI芯片,一边要求使用先进制程,一边又要求成本平衡。

这种情况下,全周围栅极(GAA)的出现,从技术层面为制程突破提供了可行解决方案,但伴随着制程复杂性的增加和制造成本的剧增。而芯片制造商要在推进技术创新的同时考虑成本和可行性,于是先进封装就成了代工厂的另一把尖刀。

恰好,这两条路径被台积电为数不多的对手三星和英特尔拿捏了。

在3nm节点,三星选择GAA以期实现追赶跨越式发展,台积电则坚守FinFET;英特尔则计划在2nm节点赶上台积电,且希望在先进封装技术上大力投入建立优势。

那么问题来了,用台积电的方式打败台积电,可行吗?

从3nm开始超车

在半导体制程技术中,2nm确实被视为可能的物理极限。因为当晶体管的尺寸缩小到这个程度时,量子效应开始变得显著,可能会导致电子的行为变得不可预测。

这种现象被称为量子隧道效应,它可能会导致电子“跳跃”到它们不应该去的地方,从而导致芯片的性能下降。

全周围栅极(GAA)晶体管是一种新型的晶体管设计,它可以在更小的制程下提供更好的性能。

在GAA晶体管中,栅极材料包围了晶体管的源和漏,从而提供了更好的电流控制。这可以帮助减少量子隧道效应,从而使得在2nm甚至更小的制程下的芯片制造成为可能。

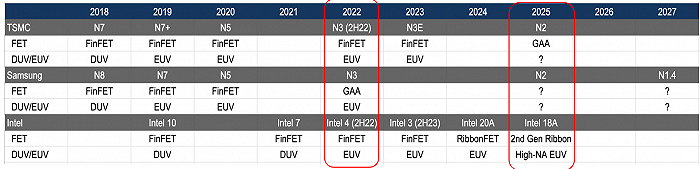

而从规划来看,台积电、三星和英特尔不约而同的搞起了制程竞速赛,虽然大的时间节点都是2022-2023年进入3nm、2025年进入2nm商业化阶段。但细微处仍有不同:

在关键的3nm节点上,三星罕见的率先量产,并且还是用更先进的GAA技术。台积电虽然随后也宣布了3nm量产,不过仍是沿用FinFET技术。

台积电总裁魏哲家的理由是,“选择沿用FinFET,是经过考虑良久,制程技术推出不是(为了)好看,是要实用,要协助客户让产品持续推进。”

当然这是略显敷衍的官方辞令,真正的原因恐怕是即便三星率先量产3nm,但因为在5nm节点能耗翻车,导致没几家客户敢吃3nm的螃蟹,只有用量相对较小的矿机芯片买家。

三星最近几年的晶圆制造处于追赶阶段,需要在3nm时代寻找技术架构差异化,拉近与台积电芯片代工方面的技术差距,用更激进的策略来获取客户。

这就给了台积电以静制动的时间差。

台积电被广泛认为是一个保守但稳定的制程技术开发者,他们倾向于确保新技术的成熟和可靠性,然后再进行部署,而不是急于将新技术推向市场。这种方法可以降低技术失败的风险,提高其芯片的产量和质量,从而确保客户的满意度。

例如,三星在2018年开始在其7nm工艺中使用EUV,然而台积电选择等待。直到EUV工具的稳定性和成熟性得到确认,以及相关问题得到解决或至少得到确定,才在2019年的N7+工艺中开始使用EUV。

这种谨慎的方法有助于台积电确保其制程技术的稳定性和可预测性,从而提供高质量的芯片给其客户。

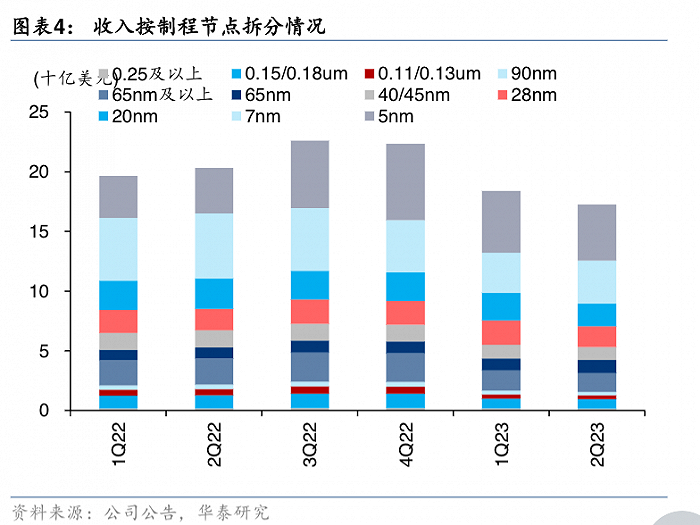

不过从时间节点上看,3nm还未能给台积电带来纸面上的收益。在最新财报里,台积电来自先进制程的收入贡献合计达53%,其中5nm的收入占比为30%,7nm为23%。

而来自券商的消息是,台积电3nm已获得全球最大客户A的订单,从2023年下半年贡献收益。明眼人一看就知道客户A是苹果,今年6月就有消息传出台积电2023年近90%的3nm产能被苹果占据。

但坏消息是,传言苹果要求台积电承担未合格芯片成本。这种情况在半导体行业非常罕见,台积电3nm初期良率大约在70%左右,苹果如果和台积电达成这样的协议,可以节省数十亿美元,但也意味着台积电的成本压力骤增。

降低制造成本

虽然大客户没有尝鲜三星的3nm,但也没用台积电。核心问题就在于,3nm的性价比实在没到一定水准。

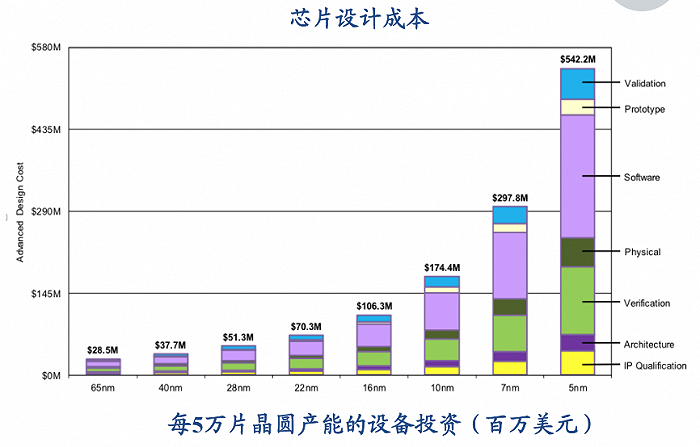

市场研究机构International Business Strategies(IBS)披露过一组数据,3nm芯片的设计费用约达5-15亿美元,兴建一条3nm产线的成本约为150-200亿美元。

这笔费用传导到代工的报价上就是:3nm工艺12英寸晶圆的报价高达3万美元,几乎是5nm工艺的一倍,7nm的三倍多。

为实现高性能计算,调整每个矢量变得越来越困难,芯片设计更加复杂,先进制程的投资额大幅提升,由此带来生产成本的抬升,以及因大尺寸芯片带来的良率问题。

在各个方面综合起来发现经济性远不如前,于是台积电、英特尔、三星等就从其他技术线路突破性能瓶颈,由此chiplet、3D先进封装等新兴方向正受到越来越高的重视。

由于单颗芯片面积越大,良率越低,相应成本越高。Chiplet也称“小芯片”或“芯粒”,它是一种功能电路块,包括可重复使用的IP块(芯片中具有独立功能的电路模块的成熟设计,也可以理解为芯片设计的中间构件)。

该技术是将一个功能丰富且面积较大的芯片裸片(die)拆分成多个芯粒(chiplet),这些预先生产好的、能实现特定功能的芯粒组合在一起,通过先进封装的形式(比如3D封装)被集成封装在一起即可组成一个系统芯片。

模块化设计思路可以提高芯片研发速度,降低研发成本。通过把大芯片分割成芯粒,可有效改善生产的良率,降低制造成本。

The Linley Group在《Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small》中提出,Chiplet技术可以将大型7nm设计的成本降低高达25%;在5nm及以下的情况下,节省的成本更大。

而上文提到的3D封装,则是代工厂们探究节省制造成本的另一种体现。

2020年,台积电将2.5D和3D封装产品整合并入一个全面的品牌3DFabric,由SoIC(系统整合芯片)、InFO(整合型扇出封装技术)、CoWoS(基板上芯片封装)所组成。

其中,InFO技术的典型产品就是iPhone 7搭载的A10芯片,而CoWoS技术则是苹果去年发布的M1 Ultra和今年发布的M2 Ultra。

具体来说,在封装这一环节,台积电将三种技术分成前、后两个阶段:

前端封装(Front-end 3D):SoIC技术是在晶圆上,将同质或异构小晶片都整合到一个类似SoC的晶片中,该晶片有更小的面积和更薄的外形。在外观上,新晶片就像普通的SoC一样,但嵌入了所需的异质整合功能。这种前端封装技术,是在设计阶段就要考量并协同设计。

由于本质就是在做一颗SoC晶片,因此只有晶圆厂可以做,且必须搭配后端封测技术不可单独存在。

后端封装(Back-end 3D):前端封装完成的SoIC晶片,必须搭配原有的立体封装技术,比如台积电的CoWoS和InFO。

而相关后端封装技术也是其他封测厂商积极跨入的领域,未必是晶圆厂独家生意。

英特尔的路数也大致相似,其先进封装技术IDM 2.0陆续推出2.5D封装的嵌入式多芯片互连桥接(Embedded Multi-die Interconnect Bridge, EMIB)技术、3D堆叠的Foveros技术,以及整合2.5D与3D封装的共嵌入式多芯片互连桥接Co-EMIB技术。

其中,Foveros封装技术利用3D堆叠整合不同的逻辑芯片,为IC设计公司提供了很大的灵活性,允许其将不同技术的IP区块与各种记忆体和I/O元件混合和搭配。

英特尔认为3D封装能延续摩尔定律,给予设计人员横跨散热、功耗、高速信号传递和互连密度的选项,最大化和最佳化产品效能。

也因此诞生了英特尔和台积电关于先进封装的投资大战:

英特尔在2.5D/3D封装领域的资本支出近两边分别达35亿/47亿美元,主要投入Foveros及EMIB等先进封装技术研发及产能扩建;

台积电在2.5D/3D封装方面已推出CoWoS及InFO等技术并进入量产,近两年资本支出达30亿/40亿美元,位居全球第二,将扩大系统整合芯片(SoIC)中多种3D Fabric平台先进封装技术推进及产能建置。

尾声

2017之前的十年,智能手机要求性能更高、面积更小、功耗更低的芯片。2017年以后HPC占比明显提升,云计算尤其是AI技术发展驱动服务器等高性能计算需求,由此诞生的一个历史转折就是:终端市场需求从智能手机转向人工智能。

但转折还未显著,体现在财报里就是台积电来自AI芯片的提振并没有多少。不过至少从目前看,台积电已经获得了先发优势,英伟达、AMD等厂商已经首选台积电合作。

甚至AMD CEO苏姿丰在媒体采访时,被问及是否将在3nm采用三星代工的产品时,直接来了一波反问:“你相信韩国媒体吗?”

参考资料

[1] 先进封装,台积电的另一把尖刀,远川研究所

[2] 台积电:寒气已经传递给我了,远川研究所

[3] 台积电Q2启示:AI增长无法弥补传统需求衰退,华泰证券

[4] 半导体行业专题研究:台积电,晶圆代工霸主从攻擂到守擂,弘则研究

[5] 3nm良率提至60%以上 三星芯片业务迎“逆风翻盘”?经济观察报

[6] 集成电路行业专题:先进制程贴近极限,Chiplet迎来黄金发展期,未来智库

[7] 台积电试产SoIC,3D封装走向量产?贤集网

评论